Contents lists available at ScienceDirect

# Journal of Network and Computer Applications

journal homepage: www.elsevier.com/locate/jnca

## Review Article

# A survey on security applications with SmartNICs: Taxonomy, implementations, challenges, and future trends

Sergio Elizalde <sup>a, b, \*</sup>, Ali AlSabeh <sup>b, b</sup>, Ali Mazloum <sup>a, b</sup>, Samia Choueiri <sup>a, b</sup>, Elie Kfoury <sup>a, b</sup>, Jose Gomez <sup>c, b</sup>, Jorge Crichigno <sup>a, b</sup>

- <sup>a</sup> Molinaroli College of Engineering and Computing, University of South Carolina, Columbia, SC, USA

- <sup>b</sup> College of Sciences and Engineering, University of South Carolina Aiken, Aiken, SC, USA

- c Katz School of Business, Fort Lewis College, Durango, CO, USA

## ARTICLE INFO

#### Keywords: SmartNIC Security applications Intrusion detection systems Volumetric attacks Privacy Threat model

## ABSTRACT

Over the last decade, network applications have grown exponentially, demanding high-speed interconnects. Unfortunately, chip manufacturers are approaching the upper limits of silicon-based computing with slow improvements in computational performance and energy efficiency. This trend has forced the industry to shift paradigms, moving from monolithic architectures to heterogeneous, domain-specific designs. Moreover, the ever-evolving threats compromise digital services and demand more scalable and flexible solutions to ensure service continuity in production networks. Smart Network Interface Cards (SmartNICs) are a product of this new paradigm, integrating domain-specific engines and general-purpose cores to offload various network infrastructure tasks, including those related to security. This paper provides a comprehensive overview of SmartNICs, with a particular focus on their role in strengthening network defenses. It introduces SmartNIC technology and presents a taxonomy of security applications offloaded to SmartNICs, categorized into Intrusion Detection and Prevention Systems (IDS/IPS), defenses against volumetric attacks, and data confidentiality mechanisms. Additionally, the paper explores vulnerabilities associated with adopting SmartNICs in the cloud, examining the threat model and reviewing proposed remediations in the literature. Finally, it discusses challenges and future trends in SmartNIC security applications, highlighting current initiatives and open research areas.

# Contents

| 1. | Introd | uction                           |

|----|--------|----------------------------------|

|    | 1.1.   | Paper contributions              |

|    | 1.2.   | Paper organization               |

| 2. | Relate | d surveys                        |

| 3. | Backgr | round                            |

|    | 3.1.   | Evolution of NICs                |

|    |        | 3.1.1. Traditional NICs          |

|    |        | 3.1.2. Offload NICs              |

|    |        | 3.1.3. SmartNICs                 |

|    | 3.2.   | SmartNICs architectures          |

|    |        | 3.2.1. SoC-based                 |

|    |        | 3.2.2. ASIC-based                |

|    |        | 3.2.3. FPGA-based                |

|    | 3.3.   | On-path and off-path SmartNICs   |

|    |        | 3.3.1. On-path                   |

|    |        | 3.3.1. On-path                   |

|    | 3.4.   | SmartNIC cybersecurity landscape |

<sup>\*</sup> Corresponding author.

E-mail addresses: elizalds@email.sc.edu (S. Elizalde), ali.alsabeh@usca.edu (A. AlSabeh), amazloum@email.sc.edu (A. Mazloum), choueiri@email.sc.edu (S. Choueiri), ekfoury@email.sc.edu (E. Kfoury), jagomez@fortlewis.edu (J. Gomez), jcrichigno@cec.sc.edu (J. Crichigno).

|     |            | 3.4.1.     | Distributed security with SmartNICs                                   | 7  |

|-----|------------|------------|-----------------------------------------------------------------------|----|

|     |            | 3.4.2.     | Network segmentation and micro-segmentation                           | 7  |

|     |            | 3.4.3.     | Next-generation firewalls                                             | 8  |

|     | 3.5.       | Advance    | s in SmartNIC for security                                            |    |

| 4.  | Metho      |            | d taxonomy                                                            |    |

|     | 4.1.       | 0.0        | nethodology                                                           |    |

|     | 4.2.       |            | y overview                                                            |    |

| 5.  |            |            | on and prevention systems                                             |    |

| ٥.  | 5.1.       |            | e-based                                                               |    |

|     | 3.1.       | 5.1.1.     | Background                                                            |    |

|     |            | 5.1.2.     |                                                                       |    |

|     |            |            | Literature                                                            |    |

|     | <b>5</b> 0 | 5.1.3.     |                                                                       |    |

|     | 5.2.       |            | r-based                                                               |    |

|     |            | 5.2.1.     | Background                                                            |    |

|     |            | 5.2.2.     | Literature                                                            |    |

|     |            | 5.2.3.     | Comparison and limitations: anomaly-based IDS/IPS                     |    |

|     | 5.3.       |            | son with programmable switches: IDS/IPS                               |    |

|     | 5.4.       |            | summary and lessons learned                                           |    |

| 6.  | Volum      |            | ks                                                                    |    |

|     | 6.1.       | Heavy h    | itter                                                                 | 14 |

|     |            | 6.1.1.     | Background                                                            | 14 |

|     |            | 6.1.2.     | Literature                                                            |    |

|     |            | 6.1.3.     | Comparison and limitations: heavy hitter                              | 15 |

|     | 6.2.       | DDoS       |                                                                       |    |

|     |            | 6.2.1.     | Background                                                            | 15 |

|     |            | 6.2.2.     | Literature                                                            |    |

|     |            | 6.2.3.     | Comparison and limitations: DDoS defenses                             | 16 |

|     | 6.3.       | Compari    | son with programmable switches: volumetric defenses                   |    |

|     | 6.4.       |            | ric attacks: summary and lessons learned                              |    |

| 7.  |            |            | confidentiality                                                       |    |

|     | 7.1.       |            | and anonymity                                                         |    |

|     | ,          | 7.1.1.     | Background                                                            |    |

|     |            | 7.1.2.     | Literature                                                            |    |

|     |            | 7.1.2.     | Limitations and comparison: privacy and anonymity                     |    |

|     | 7.2.       |            | aphy and security protocols                                           |    |

|     | 7.2.       | 7.2.1.     | Background                                                            |    |

|     |            | 7.2.1.     | Literature                                                            |    |

|     |            | 7.2.2.     | Limitations and comparison: cryptography and security protocols       |    |

|     | 7.0        |            |                                                                       |    |

|     | 7.3.       |            | son with programmable switches: anonymity and confidentiality         |    |

| 0   | 7.4.       |            | ntiality and anonymity: summary and lessons learned                   |    |

| 8.  |            |            | rabilities                                                            |    |

|     | 8.1.       |            | nodel                                                                 |    |

|     | 8.2.       | -          | rty modules                                                           |    |

|     | 8.3.       |            | nant and virtualization                                               |    |

|     | 8.4.       |            | bypassing                                                             |    |

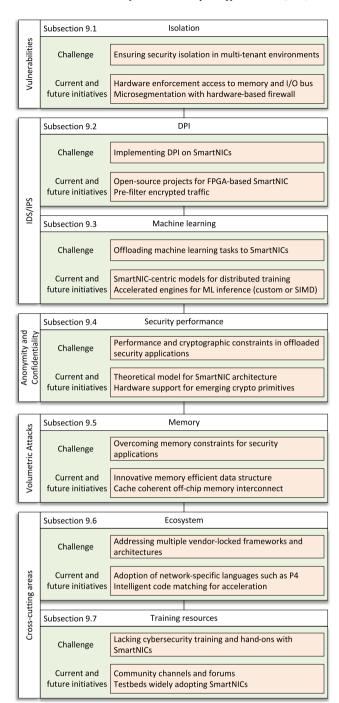

| 9.  |            |            | uture trends                                                          |    |

|     | 9.1.       |            | security isolation in multi-tenant environments                       |    |

|     | 9.2.       | _          | nting DPI on SmartNICs                                                |    |

|     | 9.3.       | Offloadii  | ng machine learning tasks to SmartNICs                                | 25 |

|     | 9.4.       |            | ance and cryptographic constraints in offloaded security applications |    |

|     | 9.5.       | Overcom    | ning memory constraints for security applications                     | 26 |

|     | 9.6.       | Addressi   | ng multiple vendor-locked frameworks and architectures                | 26 |

|     | 9.7.       | Addressi   | ng gap in cybersecurity training                                      | 26 |

| 10. | Conclu     | ision      |                                                                       | 27 |

|     | CRedi7     | Γ authorsh | ip contribution statement                                             | 27 |

|     |            |            | ompeting interest                                                     |    |

|     |            |            | ts.                                                                   |    |

|     |            |            |                                                                       |    |

|     |            | -          |                                                                       |    |

|     |            |            |                                                                       |    |

#### 1. Introduction

Network security is crucial in safeguarding sensitive data and maintaining operational integrity in the digital age. As cyber threats evolve, organizations and individuals face increasing risks from cyberattacks. Implementing robust network security measures is essential to prevent unauthorized access, protect privacy, and ensure the continuity of digital services (Aslan et al., 2023). Weaknesses in network security systems create vulnerabilities that cybercriminals can exploit to access private

data or disrupt services. Recent incidents underscore the importance of strong network security. For example, the MOVEit file transfer service experienced a significant security breach in 2023, which exposed the data of around 1800 networks worldwide (Gooding, 2024).

Traditionally, middleboxes have been deployed to mitigate and safeguard networks. These devices offer high-performance guarantees, making them well-suited for enterprise networks, data centers, and wide-area networks (Sherry et al., 2012). However, they are often costly, difficult to manage, and fully proprietary, which complicates the process of upgrading their functionalities.

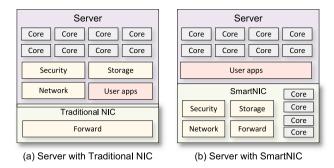

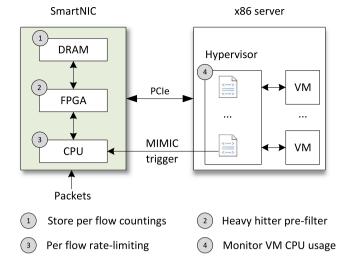

Fig. 1. Server infrastructure tasks offloaded to SmartNICs (Kanev et al., 2015). (a) In traditional setups, the server's CPU cores handle infrastructure tasks. (b) In modern data centers, SmartNICs take over these tasks, thereby saving CPU cycles on the host and isolating the server from the infrastructure execution environment.

With the rise of cloud systems, virtual security equipment has emerged as a more flexible alternative (Luo et al., 2020). This modern approach utilizes Software-Defined Networking (SDN) and Network Function Virtualization (NFV) to execute security functions on general-purpose Central Processing Units (CPUs). SDN provides centralized control and high operational flexibility due to its software-based architecture. Despite these advantages, the transition to software-driven networks results in degraded packet processing performance (Pereira et al., 2024), marked by lower throughput and higher latency. Such limitations make SDN and NFV inadequate for defending against volumetric attacks, which can escalate to several Terabits per second (Tbps) in bandwidth (Lapolli et al., 2019).

To overcome the limitations of traditional approaches, programmable data plane technologies such as programmable switches and SmartNICs have emerged. Unlike traditional fixed-function switches, programmable switches allow administrators to define custom packet processing logic using network programming languages. The de facto language used to define the behavior of packet processing is the Programming Protocol-Independent Packet Processors (P4) (P4 Language Consortium, 2024). This flexibility facilitates innovation and rapid testing of new security solutions, making programmable switches a focal point in the research for network security applications (AlSabeh et al., 2022b; Chen et al., 2023). Following the same design principles as programmable switches, the programmability of packet processing has, in recent years, been extended to Network Interface Cards (NICs), resulting in the evolution of SmartNICs. These devices integrate domain-specific processors with general-purpose CPUs, enabling developers to program applications on the SmartNIC's CPU while offloading and accelerating specific tasks using specialized engines, such as encryption, compression, and packet filtering. This combination delivers substantial performance gains while reducing the computational burden on the host system (Xing et al., 2023).

The rising adoption of SmartNICs is clearly reflected in the global information technology ecosystem, where hyperscalers, such as Google, Amazon, and Microsoft, are designing custom SmartNICs to offload infrastructure tasks, thereby optimizing operational expenditures (Firestone et al., 2018; Dancheva et al., 2024). Manufacturers like Intel, NVIDIA, and AMD are releasing SmartNIC models that integrate domain-specific processors for networking, storage, and security, along with general-purpose CPUs for enterprise and research institutions (Sundar et al., 2023; Dastidar et al., 2023).

SmartNICs are gaining increased attention in cybersecurity as they allow operators to offload networking functions from the host, thus creating hardware isolation by running infrastructure in a separate execution environment from user applications (see Fig. 1). Moreover, network security services are being deployed on SmartNICs, including Next-Generation Firewalls (NGFWs), which offer a portfolio of

Fig. 2. Proposed roadmap of the survey.

security functions such as encryption and decryption, intrusion detection and prevention, and others. Furthermore, SmartNICs can provide data provenance for various applications, such as digital twins, Machine Learning (ML) training data, and botnet detection, thus enhancing trust and fidelity across different fields (Hao et al., 2023; Seo et al., 2024). In cryptography, SmartNICs are used to test quantum-safe algorithms adopted by the National Institute of Standards and Technology (NIST) (Beckwith et al., 2023; Lawo et al., 2024). The flexibility of SmartNICs, which can be continuously reprogrammed to comply with updated security standards, allows developers to release updates rapidly and mitigate security threats without requiring a complete system redesign while maintaining both performance and cost efficiency.

#### 1.1. Paper contributions

Although SmartNICs have garnered increasing attention from both academia and industry, there is still a significant lack of comprehensive research in the area of network security. Specifically, there is no thorough survey about SmartNICs that aggregates all network security-related papers and organizes them into appropriate cybersecurity categories while simultaneously highlighting vulnerabilities and threat models. To address this gap, this paper makes four key contributions. First, it presents the advancements in SmartNICs, starting from traditional NICs, and examines how these developments enhance cybersecurity. Second, the paper introduces a taxonomy of security functions and applications offloaded to SmartNICs, detailing the techniques and methods used. Third, the paper comprehensively discusses the vulnerabilities associated with adopting SmartNICs and describes proposed solutions found in the literature, thus raising security awareness among researchers and practitioners who deploy this technology in their networks. Fourth, the paper identifies open challenges and outlines emerging trends in the SmartNIC-enabled security landscape, providing a forward-looking perspective for future research. To the best of the authors' knowledge, no previous article has provided a security-tailored comprehensive review of SmartNICs.

**Table 1**Comparison with related surveys.

| Survey                      | Tech      | nology backgro | und      |          | Taxonomy Threat Discussi |                              | ssion                                 | Focus of the |   |                      |          |

|-----------------------------|-----------|----------------|----------|----------|--------------------------|------------------------------|---------------------------------------|--------------|---|----------------------|----------|

| ourvey.                     | Evolution | Description    | Features | Overview | Literature<br>review     | Intra-category<br>comparison | Comparison with programmable switches | Challenges   |   | Future<br>directions | survey   |

| Linguaglossa et al. (2019)  | •         | ·              | 0        | 0        | 0                        | 0                            | · ·                                   | 0            | • | •                    | NFV      |

| Fei et al. (2020)           | •         | •              | 0        | •        | 0                        | •                            | •                                     | 0            | • | •                    | NFV      |

| Shantharama et al. (2020)   | •         | •              | 0        | •        | 0                        | •                            | <b>⊙</b>                              | 0            | • | •                    | NFV      |

| Freitas et al. (2022)       | 0         | •              | 0        | •        | 0                        | 0                            | 0                                     | 0            | • | •                    | OS       |

| Zheng et al. (2023)         | •         | •              | 0        | •        | 0                        | 0                            | <b>⊙</b>                              | 0            | • | •                    | ML       |

| Rosa et al. (2024)          | 0         | •              | 0        | •        | •                        | 0                            | ⊙                                     | 0            | • | •                    | General  |

| Nickel and Göhringer (2024) | •         | •              | •        | •        | 0                        | 0                            | <b>⊙</b>                              | 0            | • | •                    | General  |

| Kfoury et al. (2024)        | •         | •              | •        | 0        | 0                        | ⊙                            | ⊙                                     | 0            | • | •                    | General  |

| This survey                 | •         | •              | •        | •        | •                        | •                            | •                                     | •            | • | •                    | Security |

■ Covered in this survey ○ Not covered in this survey ○ Partially covered in this survey.

#### 1.2. Paper organization

The roadmap of this survey is depicted in Fig. 2. Section 2 compares existing surveys on SmartNICs and highlights the added value of this work. Section 3 presents an overview of SmartNICs and their architectures, features, and limitations. It also describes the advancement in hardware for security and the portfolio of security functions deployed in SmartNICs. Section 4 discusses the survey methodology and describes the proposed taxonomy. Sections 5–7 collect and analyze SmartNICs applications that address network intrusion detection and prevention systems, volumetric attacks such as heavy hitters and Distributed Denial of Services (DDoS), and confidentiality of network communications. Section 8 outlines potential vulnerabilities from adopting SmartNICs in the shared cloud, and Section 9 states the challenges and future trends in network security using SmartNICs. The abbreviations used in this article are summarized in Table 11 at the end of the article.

# 2. Related surveys

Linguaglossa et al. (2019) present a survey on performance acceleration techniques for NFV. They analyze the methods to scale and remove inherent bottlenecks in the deployment of network functions such as Network Address Translation (NAT), firewalls, and mobile functions. Moreover, the authors describe the commonly used primitives offloaded to SmartNICs and discuss how programmability increases the flexibility demanded by NFV applications. This survey briefly discusses the NGFW application deployed in SmartNICs, but it is still missing many other security applications that can be offloaded to it with a particular focus on SmartNIC.

Fei et al. (2020) analyze the performance challenges in general-purpose servers and summarize the typical performance bottlenecks when offloading NFVs. The authors review the progress in NFV acceleration and introduce a new taxonomy of state-of-the-art efforts based on various acceleration approaches. The authors discuss the surveyed works, identifying the advantages and disadvantages of each category. They also examine the products, solutions, and projects emerging in the industry. The authors also identify applications that can be implemented with SmartNICs. Additionally, they present a gap analysis to improve current solutions and highlight promising research trends for future exploration. The survey primarily focuses on NFV deployed in hardware accelerators, not including security applications of SmartNICs.

Shantharama et al. (2020) present a comprehensive survey covering commercial network accelerators and relevant research studies. The survey demonstrates that hardware acceleration can offload tasks from the general-purpose CPU and enhance its capabilities through coprocessing. The authors categorize their findings into CPU hardware accelerations, memory enhancements, and interconnect improvements (including on-chip and chip-to-chip connections). They also examine hardware-accelerated infrastructures like SmartNICs, which connect general-purpose CPU platforms to networks. In terms of security, the

survey covers acceleration for encryption and decryption in CPU architecture. Also, the poor isolation of NFV is discussed in virtual environments, such as kernel or user space applications. However, the survey does not address SmartNIC's security applications and benefits for overcoming these challenges.

Freitas et al. (2022) present a systematic review of accelerating technologies for fast network packet processing in Linux environments. When handling network packets, they identify the existing overheads and bottlenecks in the Linux kernel. The review introduces a taxonomy of fast packet processing solutions categorized into hardware, software, and virtualization. The authors then discuss these solutions in terms of host resource usage, high packet rates, system security, and flexibility. The survey discusses kernel security, isolation, and DoS over the Peripheral Component Interconnect Express (PCIe) link between Virtual Machines (VMs); however, it lacks literature on security and SmartNIC applications.

Zheng et al. (2023) discuss various in-network ML solutions developed using P4-programmable devices, including SmartNICs. They explore different ML models implemented within the network and examine the related challenges and solutions. In the survey, the authors presented various ML algorithms in programmable data planes and explained the implementation challenges. The authors emphasize that in-network machine learning can greatly enhance cloud computing and next-generation networks. The survey concludes with a discussion of future trends in this area. The survey focuses on ML techniques and some applications of inference for anomaly detection in P4 switches, rather than SmartNICs.

Rosa et al. (2024) review recent research efforts aimed at enabling cloud platforms to offer network acceleration as a service. It focuses on technologies such as eXpress Data Path (XDP), Data Plane Development Kit (DPDK), and Remote Direct Memory Access (RDMA), which are implemented with SmartNICs. The paper identifies four key aspects critical to integrating acceleration options in cloud computing: access interfaces, virtualization techniques, serviceability, and security. The survey discusses the security implications of network acceleration in public clouds, focusing on confidentiality, integrity, authentication, access control, and isolation, but it misses IDS/IPS applications, volumetric attacks, and the SmartNIC threat model assessment.

Nickel and Göhringer (2024) propose a taxonomy for programmable network devices, including SmartNICs, FPGAs, and switches. The survey emphasizes these devices' architectural characteristics and data processing capabilities in the context of in-network computing. Particular attention is given to FPGAs, analyzing their strengths and weaknesses in terms of power efficiency and acceleration capabilities. The taxonomy introduces three main categories: network device type, programming language/model, and data plane architecture. The programming model considers the development frameworks and languages used for network devices, while the network device type distinguishes between NICs and switches. The architecture has three subcategories: programmable ASICs, reconfigurable hardware, and System-on-Chip (SoC) designs. Regarding security, the survey briefly discusses IDS/IPS

systems in FPGA-based SmartNICs and highlights encryption research directions for these systems.

The closest work to ours is a recent survey on SmartNICs by Kfoury et al. (2024). The survey begins with the evolution of legacy NICs and the technological drivers behind the emergence of SmartNICs. Then, the survey reviews the available SmartNIC hardware architectures and examines open-source and vendor-specific development environments for SmartNICs. Additionally, a taxonomy is presented to classify the literature based on security, network, and compute functions offloaded to SmartNICs.

The novelties of our work pertaining to security, and compared to Kfoury et al. (2024), are:

- Our work presents a security-focused taxonomy that covers a broader application landscape, including volumetric attacks (heavy hitters, DDoS), anomaly-based IDS/IPS systems implemented using Smart-NICs, and privacy-preserving mechanisms, all mapped specifically to SmartNIC-enabled architectures.

- The authors in Kfoury et al. (2024) present a generic overview of SmartNIC applications. Although they discuss SmartNIC security-related work, the treatment of this topic is relatively brief and does not cover relevant ongoing research. Our survey is more granular and it thoroughly examines a broad range of security literature. For example, in IDS/IPS, various techniques have evolved to detect malicious activities, including signature-based and anomaly-based systems, each leveraging different techniques using SmartNICs.

- Our survey uniquely discusses the inherent security risks and attack surfaces introduced by SmartNICs themselves, which are crucial for system architects and practitioners. We complement this by analyzing remediation techniques proposed in the literature.

- The survey outlines key open research directions at the intersection

of SmartNICs and network security, extracted from the reviewed

literature and thoroughly annotated with ongoing efforts and future

trends. These directions include topics such as isolation in multitenant environments, performance modeling and quantification, and

addressing challenges across heterogeneous ecosystems.

Table 1 provides a comparative analysis of existing surveys, delineating key distinctions relative to the scope and contributions of this survey. In contrast to prior surveys, we focus on the recent advances in network security and SmartNICs. Additionally, we consider programmable switches as a precursor of SmartNICs and highlight their different applications and use cases in network security. We believe that our review can help a variety of readers understand why emerging network security techniques are increasingly choosing SmartNICs, and highlight future research directions on that topic.

# 3. Background

# 3.1. Evolution of NICs

Before exploring security applications, it is important to understand the foundational concepts of SmartNICs, including their evolution, architectures, and role in distributed security. Over the past two decades, NICs have progressed from traditional designs to Offload NICs and, more recently, to programmable SmartNICs. This evolution has enabled more efficient data processing and enhanced security capabilities. Table 2 summarizes the key characteristics of these NIC types.

# 3.1.1. Traditional NICs

Traditional NICs, also known as standard or basic NICs, are hard-ware components that connect a computer to a network. These devices implement fundamental physical and data-link layer services, including frame serialization/deserialization, link access management, and communication error detection. Typically, these functions are performed by a dedicated fixed-function component on a dedicated chip within

the NIC. On the transmitting side, the fixed-function component takes a datagram from the host, encapsulates it in a link-layer frame, and transmits the frame over the communication link according to the link-access protocol. On the receiving side, the component receives the frame and forwards it to the host via a PCIe bus. A traditional NIC has the following features:

- Basic packet processing: Traditional NICs primarily focus on moving data packets between the network and the host system's CPU. They have limited processing capabilities and rely heavily on the host CPU to handle networking tasks.

- Simple protocol handling: These NICs manage basic protocols like Ethernet and Internet Protocol (IP) but do not offload complex processing tasks from the CPU.

- Limited customization: Traditional NICs are generally fixed-function devices with minimal scope for customization or programmability.

## 3.1.2. Offload NICs

Offload NICs integrate hardware acceleration engines to execute basic infrastructure functions that were previously managed by the network stack in the host. The goal is to free up host CPU cycles and enhance the performance. Examples of such functions are:

- TCP offload engine: Offload NICs often include a Transmission Control Protocol (TCP) offload engine that handles TCP/IP processing tasks, reducing the load on the host CPU and leaving more resources for end-user applications.

- Checksum offloading: These NICs can compute checksum for data packets, saving CPU clock cycles.

- Basic packet filtering: They can perform simple packet filtering and classification to improve network performance and security.

# 3.1.3. SmartNICs

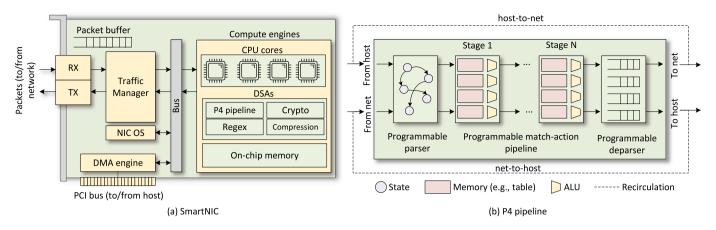

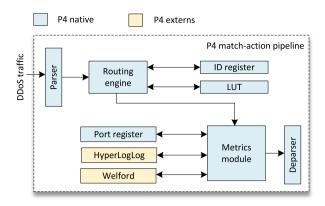

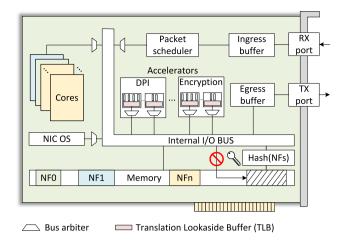

SmartNICs represent the latest advancement in NIC technology. Although there is no consensus on the definition of SmartNICS, NICs that perform functions beyond basic packet processing and have programmable elements may be considered SmartNICs. These devices are SoCs which typically have their own Operating System (OS), onchip memory, general-purpose CPU cores, and programmable Domain-Specific Accelerators (Dally et al., 2020) (DSAs), see Fig. 3(a). Typical DSAs within the SmartNIC include a P4 pipeline for packet header processing, a cryptographic accelerator for encryption/decryption operations, a regular expression accelerator for pattern matching, and a compression accelerator for compression/decompression operations. Incoming packets are received (RX) and moved to the traffic manager. The packet may then be processed by one or more DSAs, as programmed by the engineer. If the packet is directed to the host device the SmartNIC is attached to, then it is forwarded via the PCI bus. Otherwise, the packet is sent to the network (TX). Fig. 3(b) shows an example of a DSA, the P4 pipeline. This accelerator processes packet headers and consists of the following components: programmable parser, programmable match-action pipeline, and programmable deparser. The programmable parser allows the developer to define packet headers based on custom or standard protocols and parse them. It is represented as a state machine. The programmable match-action pipeline executes the operations over the packet headers and intermediate results. A single match-action stage has multiple memory blocks (tables, registers) and Arithmetic Logic Units (ALUs), which allows for simultaneous lookups and actions. Since some action results may be needed for further processing (e.g., data dependencies), stages are arranged sequentially. The programmable deparser assembles the packet headers back and serializes them for transmission out of the DSA. The DSA is programmed with P4, a programming language tailored to packet header processing. The main features of SmartNICs are summarized as follows:

Fig. 3. SmartNIC architecture and programmable pipeline. (a) Packets from the network arrive on the port (RX), and from the host on the PCI bus. Similarly, packets to the network are forwarded to the port (TX), and to the host on the PCI card. Packets are then handled by the traffic manager, which moves the packet to the appropriate compute engine. Compute engines include CPU cores and DSAs. (b) The P4 pipeline is a DSA designed for packet header processing, comprising a programmable parser, a match-action pipeline, and a deparser. Packets can follow different paths: from the network to the host (net-to-host), from the host to the network (host-to-net), or be recirculated through the pipeline for additional processing.

Table 2

Features of traditional/Offload/Smart NICs.

| Feature                            | Traditional NIC | Offload NIC | SmartNIC |

|------------------------------------|-----------------|-------------|----------|

| Infrastructure function separation | Low             | Medium      | High     |

| Security isolation                 | Low             | Low         | High     |

| General-purpose CPU                | No              | No          | Yes      |

| Acceleration engines               | Low             | Medium      | High     |

| Autonomous system                  | No              | No          | Yes      |

| Protocol flexibility               | Low             | Medium      | High     |

| Standardized models                | Yes             | Yes         | No       |

| Technology maturity                | High            | High        | Medium   |

- Programmability: SmartNICs feature a programmable pipeline that enables custom packet processing. This flexibility is powered by underlying hardware technologies, including Field Programmable Gate Arrays (FPGAs), Application-Specific Integrated Circuits (ASICs), and general-purpose CPU cores.

- Advanced offloading: They can offload a wide range of tasks, including encryption/decryption, load balancing, and compression/ decompression, among others.

- Enhanced security: SmartNICs can implement advanced security features, such as inline DoS mitigation, firewall functions, and IDS/IPS.

- Virtualization: SmartNICs support NFV, enabling the virtualization of network functions for more flexible and scalable network architectures.

- Autonomy: SmartNICs integrate a full network stack by running lightweight OS, thus being an independent endpoint in the network.

# 3.2. SmartNICs architectures

SmartNICs achieve their flexibility through various underlying technologies, which also define their architectural distinctions. A widely accepted definition characterizes SmartNICs as SoC-based devices that integrate computing engines and multi-core RISC architectures, such as ARM or MIPS. These architectures typically include hierarchical onchip memory, comprising Static Random-Access Memory (SRAM) and Dynamic Random-Access Memory (DRAM), and Input/Output (I/O) buses for communication with internal processing units and the host system when needed. Alternatively, SmartNICs may incorporate different combinations of FPGAs, ASICs, and CPUs, offering customizable solutions that balance flexibility, performance, and power consumption based on specific application needs.

#### 3.2.1. SoC-based

SmartNICs based on SoC architecture provide the capability to offload software components originally designed for the CPU. These SmartNICs are equipped with general ARM processors, which offer a high degree of flexibility, ease of programmability, and the ability to run new applications. An operating system typically runs on these SoC-based SmartNICs, managing NIC resources. Therefore, SoC-based SmartNICs can be considered individual computing nodes within the server, where the SmartNIC functions as an endpoint capable of controlling the full network stack. However, this architecture also brings some limitations similar to those of CPUs, such as limited parallelizability and latency overheads due to inherent architectural constraints.

# 3.2.2. ASIC-based

ASIC-based SmartNICs utilize application-specific integrated circuits or customized chips for packet processing. Typically, these SmartNICs incorporate specialized chips designed to perform a wide range of fixed security, networking, and storage functions. They are distinguished by their cost-effectiveness, energy efficiency, and high performance. However, their flexibility is limited by hardcoded functions established during the ASIC design phase. The functions can be configurable but not fully programmable due to the inherent underlying hardware technology.

#### 3.2.3. FPGA-based

Instead of hardcoding into the chip the functions for networks, the logic circuitry can be programmed using programmable hardware. An FPGA is an integrated circuit composed of programmable logic interconnects, allowing for the customization of digital circuits. FPGA-based SmartNICs are characterized by their high programmability, which enables the acceleration of network functions beyond what purely software-based implementations can achieve. Typically, developers write the entire hardware description using High-Level Synthesis languages and create the corresponding operating system drivers. However, frameworks such as P4FPGA (Wang et al., 2017) allow programmers to develop and evaluate data plane applications using P4 rather than hardware description languages. Moreover, community efforts are underway to develop complete open-source projects for FPGA-based SmartNICs (Xilinx, 2021). These SmartNICs pose challenges such as high power consumption, increased cost, and a lack of dynamic updatability. However, this type of SmartNIC is currently used in hyperscale data centers (Firestone et al., 2018) due to the adaptability to incorporate new features that were not designed at the moment of SmartNIC design.

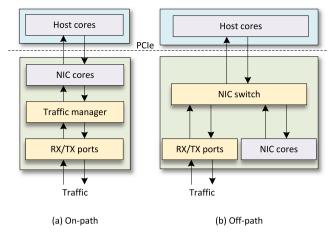

Fig. 4. On-path and Off-path SmartNICs. (a) The SmartNIC cores process all incoming traffic. (b) Traffic is steered by the NIC switch to the host or the SmartNIC according to offloaded rules.

## 3.3. On-path and off-path SmartNICs

Another approach to categorizing SmartNIC architectures is based on how their NIC cores interact with network traffic. These can be classified into two categories: on-path and off-path (Liu et al., 2019).

## 3.3.1. On-path

In on-path SmartNICs (see Fig. 4(a)), the NIC cores actively handle each incoming and outgoing packet along the communication path. These SmartNICs offer low-level programmable interfaces that directly manipulate raw packets. This design ensures the offloaded code is closely situated to the network packets, enhancing efficiency. However, this approach has its drawbacks. The offloaded code competes for NIC cores with requests sent to the host, and excessive computation offloaded to the SmartNIC can significantly degrade the performance of regular networking requests directed to the host. Typically, FPGA or ASIC SmartNICs are used to deploy on-path architecture due to their higher parallelizability, reducing the impact on the traffic.

# 3.3.2. Off-path

In this setup (see Fig. 4(b)), processing cores and memory are integrated into a separate SoC positioned adjacent to the NIC cores. The offloaded code is strategically positioned outside the critical path of the network processing pipeline. The SoC operates as an independent, fully functional end-point host with its network interface, connected to the NIC cores and the main host via an embedded switch, often referred to as a traffic manager. Depending on the forwarding rules set on the NIC switch, traffic is directed either to the main host or the SmartNIC cores. Unlike on-path SmartNICs, the offloaded code in offpath SmartNICs does not affect the host's network performance. This distinct separation allows the SoC to run a complete operating system (e.g., Linux) with a full network stack, simplifying system development and enabling offloading of complex tasks.

# 3.4. SmartNIC cybersecurity landscape

The disaggregation of networked systems (Shan et al., 2022) is redefining security architectures in modern data centers. SmartNICs enable port-level network intelligence, allowing security functions to be distributed across the infrastructure rather than centralized at perimeter devices. This is particularly relevant given the increasing volume of east—west traffic (Cisco, 2021) and the risks posed by compromised or misbehaving applications (Khan and Nencioni, 2023).

Traditionally, firewalls have served as the first line of defense by enforcing access policies and monitoring traffic (Ingham et al.,

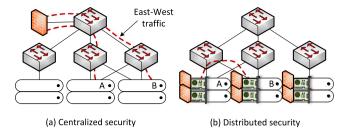

Fig. 5. Centralized vs. distributed security using SmartNICs. (a) Central appliances inspect east—west traffic but incur high overhead. (b) SmartNICs enable distributed inspection at each server, improving scalability and performance.

Table 3

Micro and network segmentation in network security (Al-Ofeishat and Alshorman, 2023)

| Feature        | Network segmentation | Micro-segmentation   |

|----------------|----------------------|----------------------|

| Granularity    | Subnets              | Individual workloads |

| Implementation | VLAN                 | Virtual NIC/SmartNIC |

| Zero-trust     | Not supported        | Supported            |

| Scalability    | Low                  | High                 |

| Complexity     | High                 | Low                  |

2002). However, they are often deployed at the network perimeter, leaving intra-network communication largely unmonitored. To address this, the evolution of firewalls has moved toward distributed models, where enforcement shifts from centralized appliances to the server's NIC. SmartNICs play a critical role in this transition by offloading Next-Generation Firewall (NGFW) functions and enabling deep packet inspection (DPI), intrusion detection/prevention systems (IDS/IPS), and authentication at the edge (Liang and Kim, 2022; Rivitti et al., 2024).

# 3.4.1. Distributed security with SmartNICs

Traditional, centralized firewalls inspect traffic at a single choke point, often introducing performance bottlenecks and traffic tromboning. In contrast, distributed firewalls push enforcement to the edge, closer to the workloads, using SmartNICs. Fig. 5 illustrates this shift from centralized to distributed inspection.

Distributed firewalls enable context-aware, workload-level policies that improve visibility and eliminate single points of failure. Smart-NICs act as enforcement points, inspecting traffic inline and executing policies with minimal latency. This architecture is particularly suitable for virtualized and multi-tenant environments where performance, scalability, and isolation are critical (Yang and Chang, 2023).

# 3.4.2. Network segmentation and micro-segmentation

Network segmentation is a widely used defensive strategy that reduces an attacker's ability to move laterally. While traditional segmentation divides traffic at the subnet level (e.g., via VLANs), it lacks granularity and offers limited visibility. In contrast, micro-segmentation, popularized by VMware (2014), secures workloads at a finer scale by applying security policies between internal components, even within the same subnet (Wagner et al., 2016). This approach is especially effective in cloud environments, where east–west traffic dominates.

SmartNICs enhance micro-segmentation by enabling security functions directly at the workload's NIC. This supports granular policy enforcement, improves scalability, and reduces complexity. Table 3 summarizes the key differences. Micro-segmentation offers finer control and improved security by isolating workloads individually, while traditional network segmentation operates at the subnet level with limited visibility and scalability.

Table 4

SmartNIC security services and their accelerators.

| Security services  | SmartNIC security accelerators |      |       |                |                 |     |  |  |

|--------------------|--------------------------------|------|-------|----------------|-----------------|-----|--|--|

|                    | TRNG                           | Hash | Regex | Sym.<br>crypto | Asym.<br>crypto | PKA |  |  |

| IDS/IPS            |                                |      | 1     |                |                 |     |  |  |

| MACsec             | ✓                              | ✓    |       | /              |                 |     |  |  |

| IPSec              | ✓                              | ✓    |       | /              | ✓               | 1   |  |  |

| TLS                | ✓                              | /    |       | ✓              | ✓               | 1   |  |  |

| Storage encryption | ✓                              |      |       | ✓              | ✓               |     |  |  |

## 3.4.3. Next-generation firewalls

Hardware designers and security companies are collaborating to develop a comprehensive security portfolio for offloading to SmartNICs. Leading firewall vendors are introducing NGFW services based on VM (Cisco Systems, 2024; Juniper Networks, 2024; Fortinet, 2024). Moreover, leading vendors such as Palo Alto Networks, VMware, and NVIDIA have developed ARM-compatible products, which can now be effectively offloaded onto SmartNICs. According to Gartner Research, NGFW should have the following features: IDS/IPS, DPI, application awareness, and support inline configurations (Gartner, 2009). Nowadays, NGFW incorporates more advanced features, including encrypted traffic control, authentication, identity-based control, and data leakage protection (Neupane et al., 2018). Vendors are moving from VM implementation to tailored SmartNIC solutions to enhance performance and security isolation (Palo Alto Networks, 2024; VMware, 2023).

## 3.5. Advances in SmartNIC for security

Infrastructure tasks such as networking, storage, and security are fundamental to data centers, campuses, and enterprise networks. Due to their repetitive and specialized nature, these tasks benefit from hardware acceleration to enhance performance and reduce power consumption. While traditionally handled by general-purpose processors with specialized instruction sets (Cheng et al., 2023; Tschofenig et al., 2015), many of these functions can be offloaded to SmartNICs.

In the context of network security, common primitives, such as encryption, authentication, and integrity checks, can be accelerated using domain-specific hardware. This includes True Random Number Generators (TRNGs) for cryptographic key generation, hardware-accelerated ciphers, regex engines, hash functions, and Public Key Accelerators (PKAs) for operations like Rivest–Shamir–Adleman (RSA), Diffie–Hellman (DH), and Elliptic Curve Cryptography (ECC). These primitives support security services across various layers of the network stack (see Table 4).

SmartNICs enhance the performance of security services such as IDS/IPS, MACsec, IPSec, TLS, and storage encryption by offloading cryptographic functions to hardware accelerators. These accelerators include regex engines, hash functions, and ciphers for symmetric and asymmetric encryption. For example, IDS/IPS systems use regex and hashing to detect anomalies, while MACsec, IPSec, and TLS secure data at various layers of the network stack. Storage encryption safeguards data at rest against breaches.

Beyond standard protocols, researchers are exploring SmartNICs for custom security applications. However, identifying which functions to offload remains a challenge due to the lack of a unified programming model. Emerging solutions propose machine learning-based detection of cryptographic functions for automatic offloading (VenkataKeerthy et al., 2022).

A limitation of fixed-function accelerators is their rigidity in adapting to evolving protocols. Modern protocols like TLS 1.3 (Rescorla, 2018) require flexibility to support various algorithms. FPGA-based SmartNICs offer a solution through reconfigurability, enabling updates to cryptographic logic (e.g., replacing Salsa20 with ChaCha20) without redesigning hardware (Bernstein et al., 2008).

#### 4. Methodology and taxonomy

## 4.1. Survey methodology

This survey adopts a structured approach that begins with a broad literature review and progressively narrows the scope to focus on security applications using SmartNICs. The initial search was conducted using academic databases such as IEEE Xplore, ACM Digital Library, and Elsevier (ScienceDirect). Keywords included SmartNIC, Data Processing Unit (DPU), Infrastructure Processing Unit (IPU), programmable NIC, and network security. The search was limited to peer-reviewed papers from journals and conferences published online up to 2024. More than 50 core papers were selected, with the majority published within the last three years. The filtering focused on studies that offload network security functions and applications to SmartNICs, excluding those related to general-purpose or unrelated applications. The selected papers are categorized into distinct taxonomy groups based on the specific security functions and approaches they address. This function-driven taxonomy was derived from analyzing the primary objectives and techniques emphasized in the surveyed works. Grouping the literature in this way reflects established practices in security research and enables a clearer comparison of how SmartNICs are applied across different security domains.

## 4.2. Taxonomy overview

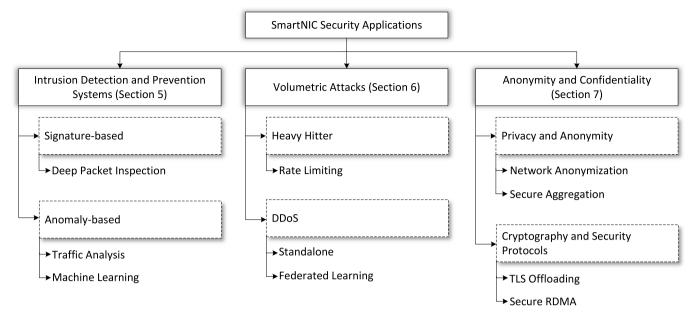

The taxonomy of SmartNICs security applications is proposed in Fig. 6. It categorizes the SmartNIC security applications into three main categories: (1) Intrusion Detection and Prevention Systems, (2) Volumetric Attacks, and (3) Anonymity and Confidentiality. These categories are not entirely orthogonal, meaning a single work may fit into multiple categories. For example, an IDS/IPS could detect and mitigate a volumetric attack. However, as volumetric attacks evolve and new approaches emerge to address them, such works are treated separately from others.

Each category provides background information on the discussed topic (e.g., DDoS, heavy hitters, etc.), giving the reader a brief introduction. This is followed by a literature review that covers relevant SmartNICs and security papers. Additionally, the subsection discusses the limitations of these approaches, providing both an intra-comparison and a comparison with programmable switches in terms of application use cases. Programmable switches are considered precursors to programmable NICs, as many design principles and frameworks have been inherited from this technology, and some works included in the taxonomy can be offloaded to both target devices.

# 5. Intrusion detection and prevention systems

The first category in the taxonomy presents applications and techniques for developing IDS/IPS using SmartNICs. The goal of IDS/IPS is to identify in real-time unauthorized use, misuse, and abuse of computer network systems by internal or external network entities and apply policies to mitigate it (Mukherjee et al., 1994). This section addresses two broad categories for IDS/IPS: signature-based and anomaly-based (Brown et al., 2002). The former leverages the programmability of SmartNICs for rules matching, and the latter includes traffic monitoring with machine learning and cooperative analysis for detecting network threats.

# 5.1. Signature-based

## 5.1.1. Background

Signature-based IDS/IPS match a set of stored rules with network traffic patterns. An alarm signal or action is triggered when the extracted traffic pattern matches an intrusion signature in the database. Examples of network signatures include source and destination IP

Fig. 6. Security taxonomy of SmartNICs based upon explored research areas.

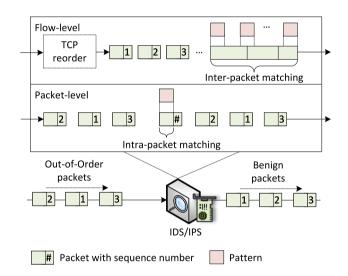

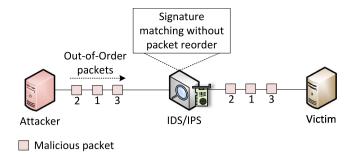

Fig. 7. Signature-based IDS/IPS using pattern matching over packet-level and flowlevel inspection. In inter-packet matching, packets have to be reordered before matching occurs.

addresses, source and destination ports, requested Uniform Resource Locators (URLs), and protocol used, among others (Kumar and Sangwan, 2012). Well-known network security tools include a form of signature-based scheme such as NetSTAT (Vigna and Kemmerer, 1998), Snort (Roesch et al., 2011), and Suricata (Suricata, 2021). This software can run either in IDS mode (passive) or IPS (active) mode. In passive deployment, traffic is copied to the IDS and inspected. In active deployment, the IPS inspects the real traffic, which can forward or drop the packets based on the matching rules (Mukhopadhyay et al., 2011).

DPI is a widely used technique in modern security infrastructure that enables SmartNICs to implement signature-based IDS/IPS (Thinh et al., 2012; Orosz et al., 2018). The core purpose of DPI is to assemble and check application layer content by inspecting the packet's payload (Arshad et al., 2023). Fig. 7 shows how the matching pattern works at the packet-level and flow-level, also named stateless and stateful DPI, respectively. Signature-based IDS/IPS could detect malicious traffic by searching fixed strings or patterns in the payload. A pattern is defined by regular expressions, which are notations that describe a set of strings

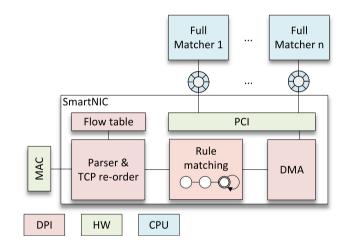

**Fig. 8.** High-level DPI architecture for IDS/IPS using FPGA-based SmartNICs (Chen et al., 2022). The SmartNIC matches sub-rules in a reduced graph. If a match exists, packets are forwarded to the CPU to complete the signature matching.

without explicitly enumerating them. Among the classical string matching algorithms, the most popular is the Aho–Corasick (AC) (Aho and Corasick, 1975), which can handle multiple patterns and guarantees  $\mathcal{O}(n)$  time complexity for an input string of n bytes. This algorithm creates a DFA based on the input strings, thus consuming more memory as the number of rules increases (Pao et al., 2010).

Due to their reconfigurable architecture, FPGA-based SmartNICs are widely used for accelerating Deep Packet Inspection (DPI) in IDS/IPS systems. As shown in Fig. 8, packets are received at the SmartNIC and passed through a processing pipeline that extracts headers and reassembles flows based on TCP sequence numbers. The reassembled packets are then checked against DPI rules using hardware-implemented state machines for high-speed pattern matching. Matching results are forwarded to the host CPU for further inspection or action.

# 5.1.2. Literature

Leveraging a decision tree model, Jia et al. (2022) propose a high-performance Access Control List (ACL) engine on an FPGA-based Smart-NIC. The rules—matching on source/destination IP addresses and ports

are compiled into decision trees that are stored in the FPGA's on-chip SRAM. To accommodate deep and unbalanced tree structures, the trees are partitioned into subtrees and mapped across distributed memory interfaces, maximizing memory bandwidth utilization. A Network-on-Chip (NoC) interconnect and ring buffer are used to coordinate packet scheduling and ensure in-order delivery despite varying tree traversal latencies. This design enables the engine to sustain a throughput of up to 250 Mpps on rule sets of 100K entries. Building on this design, Xin et al. (2024) extend the FACL architecture by introducing HACL, a heterogeneous and modular ACL engine that separates decision tree traversal from rule matching. This separation enables a more structured and scalable pipeline, reducing architectural complexity by eliminating the need for recirculating paths and NoC-based scheduling. HACL maintains support for diverse decision tree algorithms (e.g., CutSplit, HyperCuts) and large rule sets without requiring FPGA reconfiguration. It achieves over 260 Mpps throughput on 100K-rule ACLs while reducing the memory footprint to approximately 2 MB through compact rule encoding and efficient engine utilization.

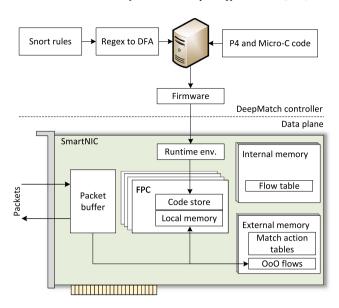

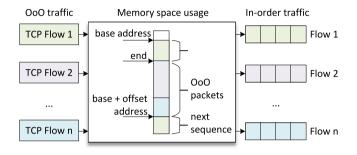

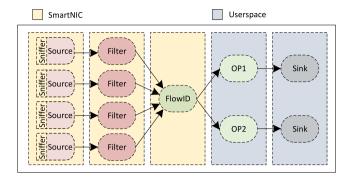

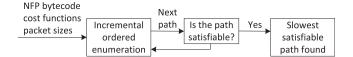

While the work in Jia et al. (2022) and Xin et al. (2024) achieves a flexible, high-performance ACL engine, it does not provide DPI functionality of signature matching on headers fields beyond the transport layer (i.e., payload). DeepMatch (Hypolite et al., 2020) presents a line rate DPI primitive in the data plane using a Netronome NFP-6000 SoCbased SmartNIC, showcasing the IDS application using Snort rules and QoS applications using Redis dataset. It transforms the regex rules and compiles them into deterministic finite automata (DFA) based on the AC algorithm. In IDS/IPS applications, it is a requirement to support TCP re-assembling for out-of-order (OoO) packets. DeepMatch supports both stateless intra-packet and stateful inter-packet regex matching capabilities. An updated per-flow state table is required for the latter since the packets have to be buffered and wait for serialization. The implementation details are depicted in Fig. 9. Incoming packets are buffered and dispatched to worker threads on the Flow Processor Cores (FPCs). When flow-level matching is desired, OoO packets are sent to a large external memory until they can be processed. The DeepMatch algorithm is natively implemented in Micro-C for the Netronome platform and integrated into the P4 processing pipeline with the help of P4 externs. The DFA memory maps and code are loaded using a runtime environment. DeepMatch can achieve 40 Gigabits per second (Gbps) in stateless mode and 20 Gbps in stateful mode.

Alternatively, researchers developed complete frameworks for signature-based IDS/IPS using FPGA-based SmartNICs. Pigasus (Zhao et al., 2020) implements IDS/IPS entirely in an FPGA-based SmartNIC. The architecture is mainly composed of a packet buffer, a parser, a reassembler module, a multi-string pattern matcher, and a DMA engine to move data from the SmartNICs to the CPU (see Fig. 8). This system mimics the NIC functionalities, such as primary packet processing, flow management, and data exchange with the host. Pigasus implements the packet reordering module for stateful pattern matching, similar to DeepMatch. It is performed to apply string matching on OoO packets. Pigasus leverages hierarchical filters to make its patternmatching memory efficient. When a match is encountered, the system sends the suspicious traffic to enter full match expression mode in the CPU. It uses a memory-dense linked list data structure to track the flows and wait for serialization (see Fig. 10). Additionally, the TCP reordering module for OoO packets separates in-order, and OoO flows to improve performance, thereby avoiding additional latency for already in-order packets. Pigasus outperforms Snort running on a CPU, offering a 3x improvement in latency and requiring 65x fewer cores to maintain a 100 Gbps throughput.

Hu et al. (2023) present a real-time malicious traffic detection with the same capability of inspecting OoO packets using an FPGA-based SmartNIC. Similarly to previous works, the core functions are the TCP OoO reassembly and a hierarchical packet match. However, this work uses a Non-deterministic Finite Automata (NFA) instead of a DFA to compute the packet matching. A key insight shown in this work relates

Fig. 9. DeepMatch is implemented on NFP-6000 to enable DPI by translating regex rules into DFAs that can be pushed to the data plane. DeepMatch uses internal and external memory to store packets that are out of order before it applies string-matching rules (Hypolite et al., 2020).

to the power consumption of every module in Fig. 8. The TCP reorder module consumes 50% of the total SmartNIC power, indicating that the hardware implementation of reordering is costly compared to the other modules.

Cheng et al. proposed Fidas (Chen et al., 2022), an FPGA-based IDS/IPS system. Following a similar approach to Pigasus, Fidas aims to develop an FPGA-based intrusion detection system that fully offloads rule pattern matching while introducing a novel traffic flow rate classification to the SmartNIC. Like Pigasus, Fidas employs a hierarchical pattern-matching approach but innovates in rule analysis and decomposition. The pattern-matching module uses a multi-level filter-based method for efficient regex processing. On the other hand, the flow rate classification module utilizes a novel dual-stack memory scheme to identify hot flows under volumetric attacks, such as DDoS or heavy hitters. This helps avoid the overhead of running DPI on flows identified as part of a volumetric attack.

In parallel to FPGA-based ACL acceleration, efforts have also been made to enhance software IDS performance using SmartNIC-assisted offloading. Sheeraz et al. (2024) integrate a Napatech SmartNIC with Snort to offload packet classification and filtering, reducing the workload on the host CPU. While the full Snort ruleset remains in host memory, the SmartNIC handles early-stage packet filtering based on IP, port, and protocol fields, effectively minimizing the volume of traffic needing deep inspection. This offloading allows the system to sustain 1 Gbps throughput under realistic traffic conditions, where only a small fraction (0.01%) of packets are malicious. The filter rules deployed on the SmartNIC are lightweight, enabling line-rate processing with minimal host CPU utilization.

# 5.1.3. Comparison and limitations: signature-based IDS/IPS

Signature-based IDS/IPS systems heavily rely on hardware to match a set of rules with the packet header and payload. This process often incurs overhead, primarily due to latency caused by memory access and scarcity of memory resources. To address this issue, Jia et al. (2022) propose two techniques. The first one is to fully utilize fast memory by distributing tree allocations across multiple memory interfaces, thus increasing bandwidth and reducing latency. The second one uses a greedy optimization algorithm to optimize space consumption by mapping the trees into parallel memory spaces.

Table 5

Comparison of signature-based IDS/IPS using SmartNICs. The reported performance varies depending on several factors, including rule set size.

| Work                   | Novelty                                  | Performance                                     | Model size | Rule set     | Year |

|------------------------|------------------------------------------|-------------------------------------------------|------------|--------------|------|

| Hypolite et al. (2020) | Line-rate DPI primitive with P4          | 40 Gbps intra-packet matching                   | 4 MB       | Snort, Redis | 2020 |

| Zhao et al. (2020)     | Complete IDS/IPS in FPGA-based SmartNIC  | 100 Gbps with 100K flows and 10K rules          | 8 MB       | Snort        | 2020 |

| Chen et al. (2022)     | Detection of flow rate for DDoS attacks  | 100 Gbps for 800 bytes packets                  | 5 MB       | Snort        | 2022 |

| Jia et al. (2022)      | High-speed ACL using decision tree       | 250 Mpps with 100K ACL rules and 150 ns latency | 8.4 MB     | 4-tuple ACL  | 2022 |

| Hu et al. (2023)       | Report per module power consumption      | 3500 MB/s with 100% malicious traffic           | 2 MB       | Suricata     | 2023 |

| Sheeraz et al. (2024)  | Combining DPDK and hardware acceleration | 1 Gbps at 20K rules with low attack injection   | N/A        | Snort        | 2024 |

| Xin et al. (2024)      | Modularized ACL to decision tree         | 260 Mpps with 100K ACL rules                    | 2.56 MB    | 5-tuple ACL  | 2024 |

**Fig. 10.** Linked list memory usage is utilized for packet reordering (Hu et al., 2023). Flows with OoO packets are allocated in contiguous memory and referenced using pointers to the segment's starting position.

DeepMatch (Hypolite et al., 2020) is also sensitive to memory latency. Although the Netronome architecture features multiple cores, multithreading cannot hide the latency overhead of reading bytes of the payload allocated in the external memory. Moreover, While up to 1024 bytes of payload can be buffered in fast memory, packets exceeding this size require additional memory access, which increases latency and degrades throughput. In contrast, FPGA-based SmartNICs benefit from deterministic memory access patterns and faster on-chip Block RAM or Ultra RAM, enabling rule lookups in a single cycle. However, this performance comes at the cost of very limited memory space, typically only a few megabytes, requiring careful model sizing and optimization.

The model size of a signature-based IDS/IPS typically corresponds to the memory required to store the DFA derived from a rule set. As Table 5 shows, this size can vary significantly depending on the number and complexity of rules. For instance, DeepMatch (Hypolite et al., 2020) employs a memory hierarchy with up to 4 MB of fast on-chip memory and 2 GB of external DRAM; however, performance degrades as the model size grows and accesses to slower external memory become more frequent. FPGA-based solutions like Pigasus (Zhao et al., 2020) and Fidas (Chen et al., 2022) keep their memory usage below 10 MB to fit within local fast memory, avoiding off-chip access that would impair performance. Conversely, hybrid systems that combine software and hardware (e.g., DPDK-based solutions) may not report precise model sizes, as part of the rule matching still depends on host-side processing.

Hu et al. (2023) evaluate IDS/IPS throughput under varying attack loads, showing that performance can range from 750 MB/s to 3500 MB/s as the share of malicious traffic increases from 20% to 100%. These insights underscore the importance of balancing rule complexity, memory constraints, and real-time performance when deploying IDS/IPS on SmartNICs. Table 5 presents a comparative overview of representative works, summarizing their novelty, throughput, model size, and rule configuration.

# 5.2. Anomaly-based

## 5.2.1. Background

Generally, signature-based schemes have excellent detection accuracy for previously known intrusions. However, new vulnerabilities, also known as zero-day attacks, continue to emerge (Ahmad et al., 2023). These include threats with unseen signatures that have not yet

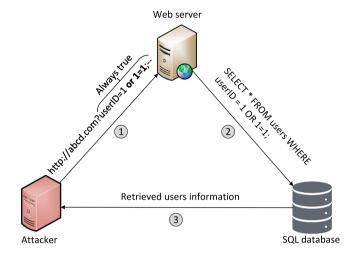

Fig. 11. Boolean-Based In-Band SQL Injection Attack. The attacker sends a crafted HTTP request containing a malicious condition (1 OR 1=1) that always evaluates to true (1). The web server incorporates this input into an malicious SQL query and forwards it to the database (2), which processes the query and returns all user records (3). The attacker then receives the retrieved data, effectively bypassing authentication and gaining unauthorized access.

been cataloged. Anomaly-based IDS/IPS systems offer an alternative by analyzing traffic behavior rather than relying on predefined signatures (Jyothsna et al., 2011). In these systems, legitimate system behavior is modeled using machine learning, statistical, or knowledge-based methods. Any significant deviation from the established model is flagged as an anomaly, which can then be classified as an intrusion (Scarfone et al., 2007). This approach assumes that malicious behavior differs measurably from normal user activity.

A concrete example is the detection of SQL injection (SQLi) attacks, where anomaly-based systems can identify abnormal database query patterns that deviate from expected application behavior. As illustrated in Fig. 11, an attacker can craft a malicious input (e.g.,  $1\ OR\ 1=1$ ) embedded within an HTTP request, which results in unauthorized access to user records once processed by the backend database. Detecting such abnormal request patterns in real-time can help mitigate application-layer attacks like SQLi. A widely used anomaly-based IDS is Zeek (2020), which can be combined with SmartNIC-based analysis for improved visibility. When integrated with host-based defenses, Smart-NICs enable advanced threat detection by analyzing packet behavior and extracting features directly at the hardware level.

# 5.2.2. Literature

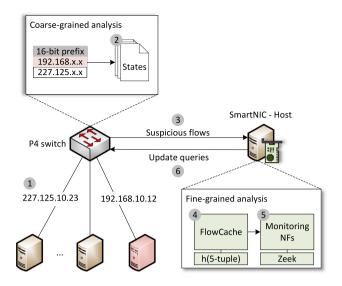

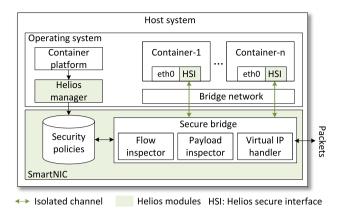

Panda et al. (2021) develop SmartWatch, a cooperative model using P4 programmable data plane switches and Netronome SmartNICs for stateful flow tracking. The collaborative monitoring scheme uses a P4 switch to identify attack indicators at a coarse granularity. It is a "bump-in-the-wire" processing approach, wherein the P4 switch passively monitors traffic, computes switch queries, and steers traffic to the SmartNIC-Host subsystem only when further inspection is required, thus avoiding benign flows to suffer from additional latency. The SmartNIC role is to accelerate and track the flow state faster than the

**Fig. 12.** High-level architecture of SmartWatch for cooperative monitoring (Panda et al., 2021). Multiple SSH connection attempts targeting a host are detected (1). P4 switch measures if the number of SSH connection attempts has been exceeded (2). Only a subset of the traffic is steered to the SmartNIC (3). These flows are tracked in a hash table created using a 5-tuple in the SmartNIC (4). Zeek monitors the malicious traffic in the SmartNIC and Host (5). The SmartNIC/Host subsystem updates the queries in the P4 switch (6).

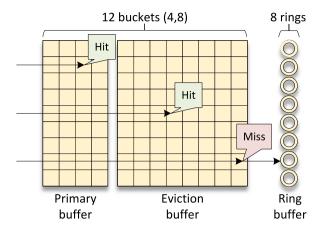

host. However, it has limited resources compared to the host in terms of both memory and processing resources. To address efficient state-tracking at high packet arrival rates, SmartWatch introduces a novel in-memory data structure and flow eviction policy on the SmartNIC. It utilizes SmartNIC's memory to design a FlowCache, comprising a hash table and ring buffers, to accommodate up to 25 million flow entries. Fig. 12 shows the proposed architecture in an SSH brute-forcing scenario. The P4 switch computes login attempts and compares them against a threshold. Only the subset of traffic that crosses the threshold is steered to the SmartNIC for further inspection in collaboration with the host. Logs are registered in the host if an anomaly is detected, and queries are updated to the switch to block the attack.

Pacífico et al. (2022) propose an IDS/IPS based on the Extended Berkeley Packet Filter (eBPF) combined with the XDP module. This approach enables the system to efficiently mitigate various types of attacks in real-time, including Structured Query Language (SQL) injection, malware, DDoS, and Peer-to-Peer traffic. The user provides the filters in a Function-as-a-Service model, executed sequentially in the hardware (i.e., SmartNIC). The scheduling algorithm follows a FIFO approach, with the SmartNIC immediately executing the first loaded filter and returning system information about the program's status to the user. Other filters are stored in a queue until the preceding filter completes execution. The filters, written in C, may include regex operations to detect specific attacks. The system achieves 10 Gbps for different filters, and the requests for adding a filter to the scheduler are about 500 ms and 900 ms on average, representing a significant overhead.

SmartNICs can be leveraged to deploy ML-based approaches to detect malicious behavior. Tasdemir et al. (2023) implement a SQL injection detector based on classical machine learning algorithms in the NVIDIA Bluefield-3 SmartNIC. Typically, specialized models are utilized for language detection and analysis, such as Natural Language Processing (NLP) (Gowtham and Pramod, 2021). However, SmartNICs lack the ML accelerators to run real-time complex models. Instead, several classical machine learning models, such as XGBoost and K-nearest neighbors, have been tested. Among the classifiers, the Passive Aggressive Classifier (Crammer et al., 2006) achieved the highest accuracy, scoring over 98%, outperforming all other models tested.

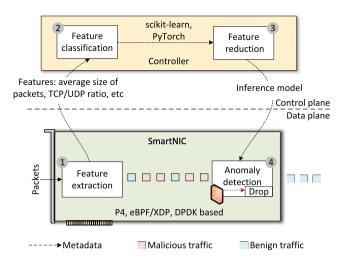

Fig. 13. In-network machine learning architecture for anomaly-based IDS/IPS using SmartNICs. Depending on the protocol, relevant packet fields, and metadata are extracted to add features (1). These features are then classified using supervised learning (2). Then, to reduce memory expenditure, the ratio of filtering rules and dropping benign traffic is optimized (3). The model is offloaded to the data plane, where it transmits or drops the packet according to the classification (4).

Xavier et al. (2021) developed an IDS based on decision trees implemented in P4 on Netronome SmartNICs. Using P4 to deploy the machine learning algorithm directly into the data plane drastically enhances such a system's performance. To overcome the limitations of the P4 language, which has limited computation capabilities, the authors translated the decision tree trained to a series of if-else statements that can be encoded in the P4 language. Moreover, the authors report a trade-off between per-flow and per-packet classification, stating that per-packet classification provides sufficient performance for distinguishing between benign and attack traffic. However, when higher accuracy is needed to identify specific attacks, per-flow classification is required. Fig. 13 shows the general architecture of implementing ML classifiers for anomaly detection and mitigation using SmartNICs.

Wu et al. (2022) proposed ONLAD-IDS, an on-device sequential learning approach with a supervised anomaly detector. Unlike purely supervised or unsupervised learning, the semi-supervised approach uses both labeled and unlabeled data to train the classifier. Additionally, it leverages sequential learning to update the model during runtime. The ONLAD-IDS architecture includes packet sniffing, a feature extractor, feature selection using Analysis of Variance (ANOVA), and the ONLAD model. A key advantage of this model is its continuous adaptive learning, which facilitates maintaining and updating the inference model at runtime.

# 5.2.3. Comparison and limitations: anomaly-based IDS/IPS

Anomaly-based IDS/IPS systems leverage SmartNICs either for fine-grained statistics collection (e.g., SmartWatch) or to offload inference models for real-time traffic classification. These approaches vary from standalone deployments, as seen in ONLAD-IDS (Wu et al., 2022; Tasdemir et al., 2023; Xavier et al., 2021), to cooperative architectures, like SmartWatch (Panda et al., 2021), which involve programmable switches, hosts, and SmartNICs working together to improve performance and granularity.

Some works explore serverless IDS architectures, where sequential filters run on SmartNICs across multiple tenants (Pacífico et al., 2022). However, this model introduces queuing and communication delays, especially under high traffic or attack conditions, such as volumetric DoS, where delayed execution can affect mitigation effectiveness. Despite these challenges, it provides a viable approach for multi-tenant SmartNIC usage while preserving data isolation.

Table 6

Comparison of anomaly-based IDS/IPS using SmartNICs.

| Work Technique Attack vector |                   |             |          | Performance | Year |         |                                        |      |

|------------------------------|-------------------|-------------|----------|-------------|------|---------|----------------------------------------|------|

|                              |                   | Brute force | Scan     | DoS         | SQLi | Malware |                                        |      |

| Panda et al. (2021)          | Traffic analysis  | 1           | <b>✓</b> |             |      |         | 43 Mpps with 64-byte packet            | 2021 |

| Xavier et al. (2021)         | Decision tree     | ✓           | ✓        | ✓           |      |         | Above 95% and 100 ns delay             | 2021 |

| Wu et al. (2022)             | Semisupervised ML | ✓           |          | ✓           |      | ✓       | 90% detection rate and 1500 pkts/ms    | 2022 |

| Pacífico et al. (2022)       | Custom filters    |             |          | /           | ✓    | ✓       | 10 Gbps with 64-byte packet            | 2022 |

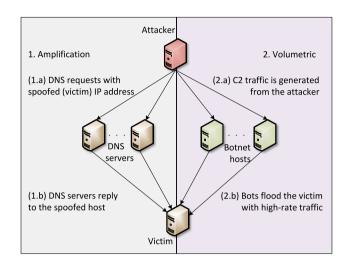

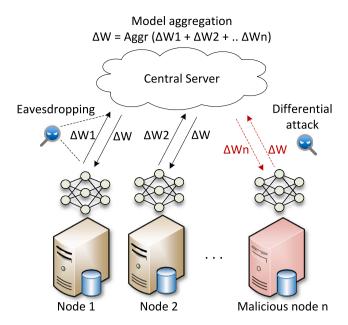

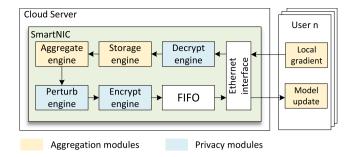

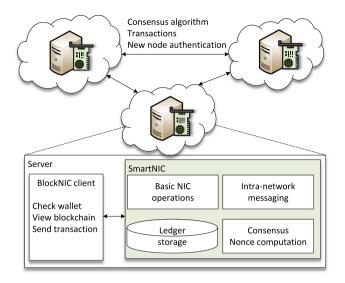

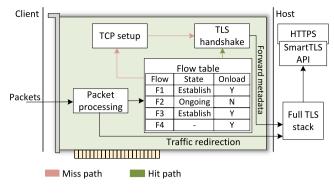

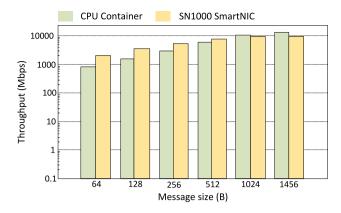

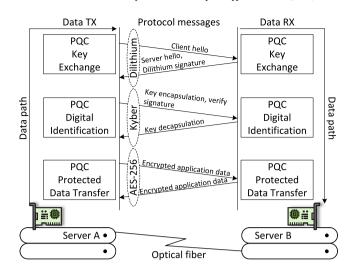

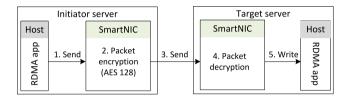

| Tasdemir et al. (2023)       | Classical ML      |             |          |             | ✓    |         | 95% detection rate and 0.0003 ms delay | 2023 |